FPGA(現(xiàn)場(chǎng)可編程門陣列)技術(shù)作為現(xiàn)代電子系統(tǒng)設(shè)計(jì)的核心,以其高度的靈活性和并行處理能力,在通信、圖像處理、人工智能等領(lǐng)域發(fā)揮著日益重要的作用。其傳統(tǒng)的設(shè)計(jì)方法往往涉及復(fù)雜的硬件描述語(yǔ)言(如Verilog或VHDL)和繁瑣的設(shè)計(jì)流程,對(duì)初學(xué)者乃至經(jīng)驗(yàn)豐富的工程師都構(gòu)成了一定的門檻。明德?lián)P至簡(jiǎn)設(shè)計(jì)法應(yīng)運(yùn)而生,旨在化繁為簡(jiǎn),提供一套高效、清晰、易于掌握的FPGA設(shè)計(jì)與開(kāi)發(fā)方法論。本教程總匯將系統(tǒng)性地闡述該設(shè)計(jì)法的核心理念、實(shí)踐步驟,并關(guān)聯(lián)其在計(jì)算機(jī)軟硬件協(xié)同開(kāi)發(fā)中的關(guān)鍵角色。

一、 明德?lián)P至簡(jiǎn)設(shè)計(jì)法的核心理念

“至簡(jiǎn)”并非意味著功能簡(jiǎn)化,而是追求設(shè)計(jì)思路與流程的極致清晰與高效。其核心在于:

- 模塊化與層次化:將復(fù)雜系統(tǒng)分解為功能明確、接口清晰的獨(dú)立模塊。每個(gè)模塊專注于單一功能,通過(guò)標(biāo)準(zhǔn)化的接口進(jìn)行互聯(lián),極大降低了系統(tǒng)整體的設(shè)計(jì)和調(diào)試復(fù)雜度。

- 模板化與模式化:針對(duì)FPGA設(shè)計(jì)中常見(jiàn)的功能單元(如狀態(tài)機(jī)、FIFO、數(shù)據(jù)流處理單元等),出經(jīng)過(guò)驗(yàn)證的、最優(yōu)化的設(shè)計(jì)模板。開(kāi)發(fā)者只需根據(jù)具體參數(shù)進(jìn)行適配,避免了重復(fù)勞動(dòng)和潛在錯(cuò)誤。

- 可視化與流程化:強(qiáng)調(diào)設(shè)計(jì)過(guò)程的可視化管理,通過(guò)清晰的流程圖、時(shí)序圖來(lái)規(guī)劃邏輯。設(shè)計(jì)流程被固化為明確的步驟(需求分析->模塊劃分->接口定義->代碼實(shí)現(xiàn)->功能仿真->綜合實(shí)現(xiàn)->板級(jí)調(diào)試),使開(kāi)發(fā)過(guò)程井然有序。

- 軟硬件協(xié)同思維:在設(shè)計(jì)初期就綜合考慮硬件(FPGA邏輯資源、時(shí)序、功耗)與軟件(驅(qū)動(dòng)、應(yīng)用程序、算法)的劃分與交互,追求整體系統(tǒng)的最佳性能與成本平衡。

二、 FPGA精簡(jiǎn)設(shè)計(jì)流程詳解(基于至簡(jiǎn)法)

- 需求分析與規(guī)格定義:明確系統(tǒng)需要完成的任務(wù)、性能指標(biāo)(如處理速度、數(shù)據(jù)帶寬、延遲)以及外部接口。這是所有設(shè)計(jì)的基石。

- 系統(tǒng)架構(gòu)與模塊劃分:根據(jù)需求,繪制系統(tǒng)框圖。將總功能劃分為數(shù)個(gè)協(xié)同工作的子模塊,例如:數(shù)據(jù)采集模塊、算法處理核心、存儲(chǔ)控制模塊、通信接口模塊等。明確定義每個(gè)模塊的輸入、輸出信號(hào)及時(shí)序關(guān)系。

- 接口標(biāo)準(zhǔn)化與協(xié)議制定:模塊間采用簡(jiǎn)單、統(tǒng)一的接口協(xié)議(如簡(jiǎn)單的握手信號(hào)、標(biāo)準(zhǔn)總線協(xié)議AXI-Stream等),這是保證模塊能夠像“積木”一樣靈活組合的關(guān)鍵。

- 模板化代碼實(shí)現(xiàn):使用Verilog或VHDL,但代碼結(jié)構(gòu)嚴(yán)格遵循預(yù)設(shè)模板。例如,狀態(tài)機(jī)采用“三段式”寫法,確保代碼清晰且綜合結(jié)果可靠。重點(diǎn)描述模塊的“行為”而非過(guò)于底層的電路結(jié)構(gòu)。

- 高效仿真驗(yàn)證:搭建分模塊和系統(tǒng)級(jí)的測(cè)試平臺(tái)(Testbench),進(jìn)行充分的仿真測(cè)試。至簡(jiǎn)法鼓勵(lì)使用自動(dòng)化腳本和斷言(Assertion)來(lái)提高驗(yàn)證效率。確保邏輯功能在進(jìn)入硬件前已基本正確。

- 綜合與實(shí)現(xiàn)約束:利用FPGA廠商工具進(jìn)行綜合、布局布線。此階段需合理添加時(shí)序、引腳、區(qū)域等約束,以確保設(shè)計(jì)能在目標(biāo)芯片上穩(wěn)定運(yùn)行于指定頻率。至簡(jiǎn)法強(qiáng)調(diào)約束文件的規(guī)范化和可重用性。

- 板級(jí)調(diào)試與驗(yàn)證:將生成的比特流文件下載到FPGA開(kāi)發(fā)板,結(jié)合邏輯分析儀(如ILA)、芯片自帶的調(diào)試內(nèi)核進(jìn)行實(shí)時(shí)信號(hào)抓取和分析,快速定位并解決問(wèn)題。

三、 與計(jì)算機(jī)軟硬件技術(shù)開(kāi)發(fā)的深度融合

FPGA從來(lái)不是孤立存在的,它通常是更大計(jì)算系統(tǒng)的一部分。至簡(jiǎn)設(shè)計(jì)法尤其注重這種協(xié)同:

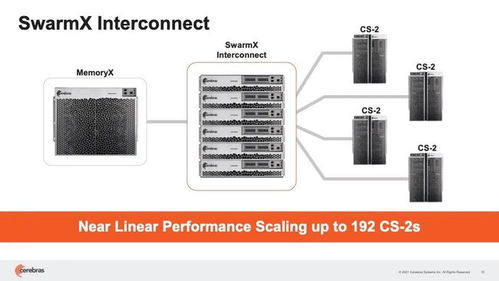

- 作為硬件加速器:在異構(gòu)計(jì)算體系中,F(xiàn)PGA常作為CPU的協(xié)處理器,用于加速特定的計(jì)算密集型任務(wù)(如加解密、視頻編解碼、神經(jīng)網(wǎng)絡(luò)推理)。至簡(jiǎn)法指導(dǎo)如何設(shè)計(jì)高效、接口標(biāo)準(zhǔn)的加速器IP,以便通過(guò)PCIe等總線與主機(jī)CPU順暢通信。

- 軟硬件接口設(shè)計(jì):設(shè)計(jì)精簡(jiǎn)而完備的寄存器配置接口(通常通過(guò)APB、AXI-Lite等總線),使得上層軟件(驅(qū)動(dòng)程序、應(yīng)用程序)可以方便地控制FPGA功能、查詢狀態(tài)、傳輸數(shù)據(jù)。這是軟硬件聯(lián)調(diào)成功的前提。

- 系統(tǒng)級(jí)建模與驗(yàn)證:在前期,可以使用高級(jí)語(yǔ)言(如C/C++、SystemC)或基于FPGA的仿真環(huán)境,對(duì)包含軟件算法和硬件邏輯的完整系統(tǒng)進(jìn)行建模和性能評(píng)估,指導(dǎo)硬件/軟件功能的合理劃分。

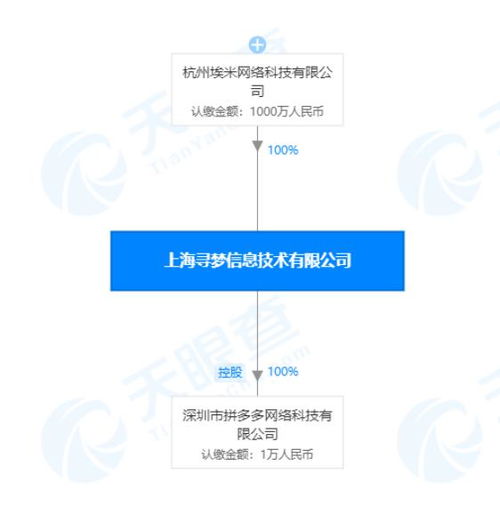

- 嵌入式SoPC開(kāi)發(fā):在集成硬核處理器(如ARM Cortex)的FPGA(如Zynq系列)上,至簡(jiǎn)法同樣適用。它指導(dǎo)如何構(gòu)建自定義的硬件外設(shè)(PL部分),并集成到處理器系統(tǒng)(PS部分)中,通過(guò)統(tǒng)一的軟件開(kāi)發(fā)環(huán)境(如Vitis)進(jìn)行應(yīng)用程序開(kāi)發(fā),實(shí)現(xiàn)真正的單芯片系統(tǒng)解決方案。

四、 與學(xué)習(xí)路徑建議

明德?lián)P至簡(jiǎn)設(shè)計(jì)法為FPGA學(xué)習(xí)者和開(kāi)發(fā)者提供了一條從入門到精通的清晰路徑。它通過(guò)將復(fù)雜問(wèn)題模塊化、將通用方法模板化、將開(kāi)發(fā)流程標(biāo)準(zhǔn)化,顯著降低了學(xué)習(xí)曲線,提升了設(shè)計(jì)質(zhì)量和開(kāi)發(fā)效率。

建議學(xué)習(xí)路徑:

1. 基礎(chǔ)入門:掌握數(shù)字電路基礎(chǔ)、Verilog語(yǔ)法。

2. 方法學(xué)習(xí):深入理解至簡(jiǎn)設(shè)計(jì)法的模塊劃分、模板代碼和設(shè)計(jì)流程。

3. 工具熟悉:熟練使用一種主流FPGA開(kāi)發(fā)工具(如Vivado、Quartus)及其仿真、調(diào)試功能。

4. 項(xiàng)目實(shí)踐:從簡(jiǎn)單項(xiàng)目(如數(shù)碼管顯示、串口通信)開(kāi)始,嚴(yán)格遵循至簡(jiǎn)流程進(jìn)行實(shí)踐。

5. 系統(tǒng)拓展:嘗試涉及軟硬件交互的項(xiàng)目,如基于MicroBlaze或Zynq的嵌入式系統(tǒng)設(shè)計(jì),或參與包含算法加速的完整系統(tǒng)開(kāi)發(fā)。

通過(guò)踐行至簡(jiǎn)設(shè)計(jì)法,開(kāi)發(fā)者不僅能高效完成FPGA邏輯設(shè)計(jì),更能培養(yǎng)出色的系統(tǒng)架構(gòu)思維,成為契合當(dāng)今軟硬件協(xié)同開(kāi)發(fā)趨勢(shì)的復(fù)合型技術(shù)人才。